大数据时代对存储器的性能提出了极高的要求,尤其是类脑计算、边缘计算急需功耗极低的存储器。在新型存储器中,相变存储器(PCM)是与CMOS工艺最兼容,技术最成熟的存储技术。2015年,Intel和Micron推出了傲腾三维相变存储芯片,速度和寿命比固态闪存硬盘要快一千倍,其三维堆叠技术也使容量高出了十倍。然而,由于在相变过程中需要将存储介质熔化冷却,导致相变存储器的功耗极高且发热严重,限制了存储容量的进一步提高,也大大增加了其制造成本。因此,降低相变存储器的功耗将便于进一步提升存储器数据密度,提高其在半导体存储市场核心竞争力,此外降低功耗可以改善存储器散热问题,减少相邻单元间的热串扰,从而提高器件稳定性和整体性能。目前最先进的几十纳米制程的单个相变存储单元擦写功耗达到了40pJ左右,而实验室制备的百纳米大小的器件功耗达到1000pJ以上。

为了解决相变存储器中高功耗的瓶颈问题,华中科技大学集成电路学院信息存储材料及器件研究所(ISMD)联合西安交通大学材料创新设计中心(CAID)研发了一种网状非晶结构的相变存储器,功耗达到了0.05pJ以下,比主流产品功耗低了一千倍。与普通“蘑菇结构”的相变存储器不同,这种新型存储器利用相变材料的自发分相在介质中形成了一些“导电岛”,而对该存储器的擦写只需要将这些岛链接或者断开即可。除了低功耗以外,该相变存储器拥有一致性好且寿命长的优点。这种结构的相变存储器在制备工艺上同样具有很大优势,到目前为止,所有降低功耗的方法都遵循功耗和数据存储设备大小之间的直接缩放,这提高了器件制备的工艺难度,而对于网状非晶结构的相变存储器提出了一种可以打破功耗与器件大小的比例依赖关系的材料设计策略,该合金可以通过溅射沉积合成,无需添加复杂的制造工艺,这为PCM单元的高密度集成提供了另一种方法。该材料设计策略使得能在一个正常尺寸的器件(250nm孔径)中产生几十个fJ的超低的擦写能耗。

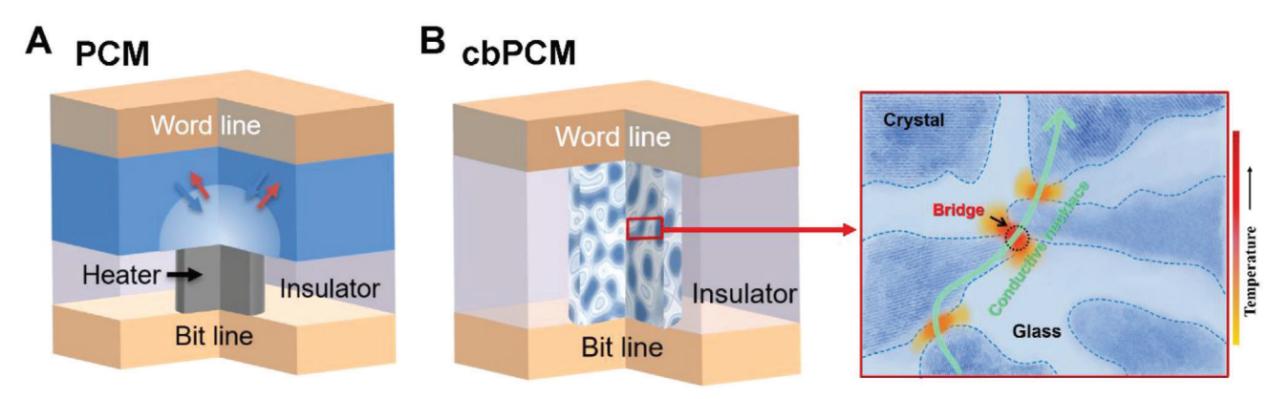

该导电桥相变存储器(Conductive-Bridge Phase-Change Memory,cbPCM)的原理是在PCM合金内部产生一个几纳米粗细的导电通道,从而使开关体积最小化且电流路径可以很容易地打开和关闭。如下图B中所示,导电通道由低电阻和低Tc(相变温度)的PCM区域组成,即连接在一起的晶体纳米区域(CNDs),它们被高电阻态的非晶态区域包围。这些CNDs几乎相互连接,只有微小的非晶间隙隔开。循环开关过程中的相变仅在CNDs之间的微小间隙中进行。换句话说,电流路径的电阻是由连接CND的小桥段控制的,通过将缺失的链路(红色区域)转换为导电桥,电流和由此产生的焦耳热很可能被集中起来,在许多CNDs上形成一条导电链。该方案利用了焦耳加热引起的界面相变,这在纳米制造模式(和掺杂)GST存储单元中被证明是可能的(将擦写电流降低到20μA)。

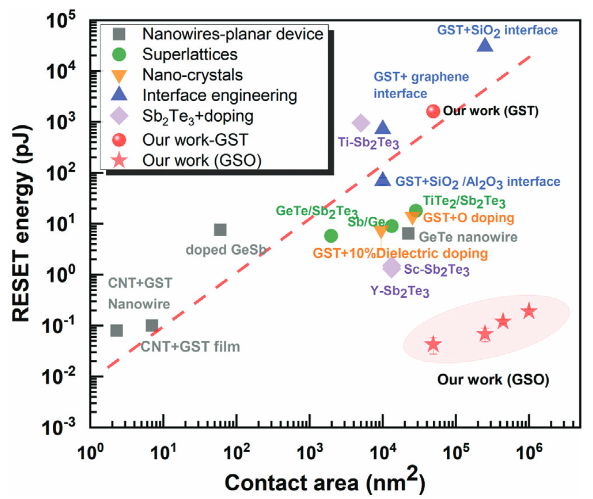

如前文所述,cbPCM的擦写能耗可以达到达到极低的几十个fJ,对于典型的PCM设备每次擦写操作需要几十个pJ到几十个nJ,cbPCM的能耗降低到了典型PCM的千分之一级别。在此工作之前,全世界功耗最低的相变存储器是由碳纳米线实现的,其擦写能耗约为100fJ,通过使用自对准的GST纳米线和CNT电极,能耗可以进一步降低到约80fJ,然而这种碳纳米线工艺要实现大规模半导体制造还需要很长的时间。下图中展示了典型PCM设备中擦写能量值与电极接触面积的关系(虚线所示),可以看到我们的基于GSO的设备具有超低编程能耗,在正常尺寸下功耗远低于典型PCM设备,打破了之前所有设备建立的功耗与电极接触面积的比例关系。因此,cbPCM的功耗和制备难度方面相比于典型PCM和碳纳米线器件都具有很大的优势。

本工作利用精心设计的GSO合金成功设计和制造了纳米级导电桥PCM器件,打破了能量大小的直接尺度相关性,达到了相变存储单元的低编程能量。该合金与目前的半导体生产线兼容,并可以实现一次性溅射,确保简单和低成本的生产。此外,该相变材料也在未来表现出更多的用途,例如基于GSO的单元也可以呈现多级电阻能力,可以通过更强的重置脉冲来增加或断开更多的连接桥,或使用更长的SET脉冲来结晶更大比例的非均匀网络,这种编程模式带来的波动和可变性可以应用在对随机相变神经突触的模拟,在生物神经网络中的信号编码和传输中起着关键作用。随着GSO单元接近生物神经电脉冲的功耗,该cbPCM器件的性能将优于传统的基于GST的PCM器件。

该成果以“Designing Conductive-Bridge Phase-Change Memory to Enable Ultralow Programming Power”为题发表在《AdvancedScience》上。论文的第一作者为杨哲博士、王疆靖博士、李博文。通讯作者为徐明教授、缪向水教授、张伟教授和马恩教授。该研究是在国家自然科学基金、国家重点研发计划和国家02专项的资助下开展的,材料的实验表征受到了中科院上海微系统所朱敏研究员的倾力相助。

文章信息:

Yang, Z., Li, B., Wang, J.-J., Wang, X.-D., Xu, M., Tong, H., Cheng, X., Lu, L., Jia, C., Xu, M., Miao, X., Zhang, W., Ma, E., Designing Conductive-Bridge Phase-Change Memory to Enable Ultralow Programming Power. Adv. Sci. 2022, 2103478.DOI:10.1002/advs.202103478

https://onlinelibrary.wiley.com/doi/10.1002/advs.202103478