2月12日,《科学进展》(Science Advances)期刊在线发表了集成电路学院缪向水、李祎团队在忆阻存算一体技术方面的最新研究成果。论文题为“Fully Analog Iteration for Solving Matrix Equations with In-memory Computing”。该工作结合了忆阻全模拟域迭代电路和数字处理器的特点和优势,构建了一套异构矩阵方程求解系统,为实现低时间复杂度、高精度、高能效的忆阻存算一体硬件提供了新方案。

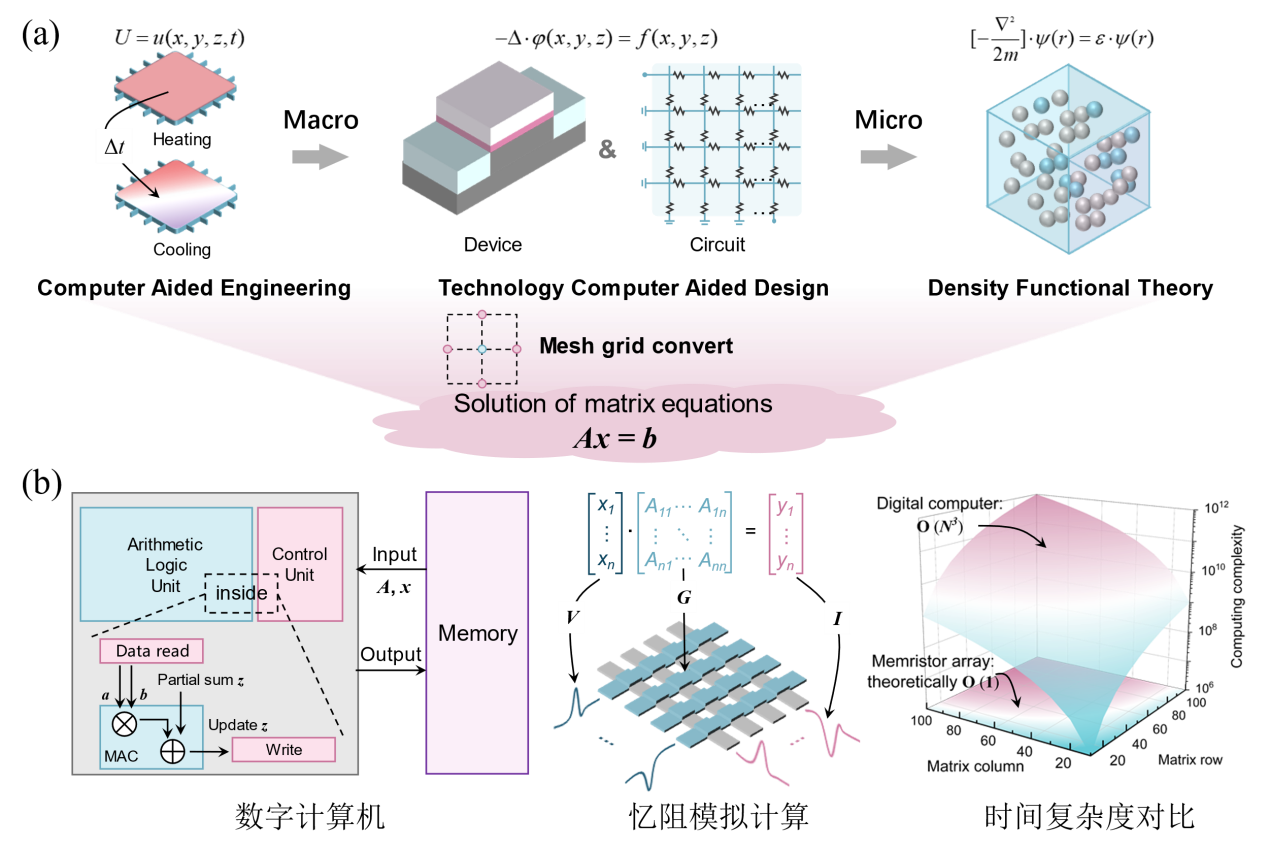

图1. (a)矩阵方程的应用场景;(b)数字计算与忆阻模拟计算的时间复杂度对比

矩阵方程求解是现代科学与工程建模的基础问题。在密度泛函计算、TCAD等实际任务中,计算机系统通常需要求解复杂的高维矩阵方程以满足建模精度需求。当前,主流数字计算机面临数值迭代算法O (N³)时间复杂度的限制以及冯·诺依曼架构瓶颈导致的算力与能效挑战。忆阻存算一体技术被视为实现高能效计算的新范式,然而国际上已报道的大部分忆阻方程求解器由于低精度模拟计算机制的限制,时间复杂度、能效和精度三个重要性能指标之间存在突出矛盾。

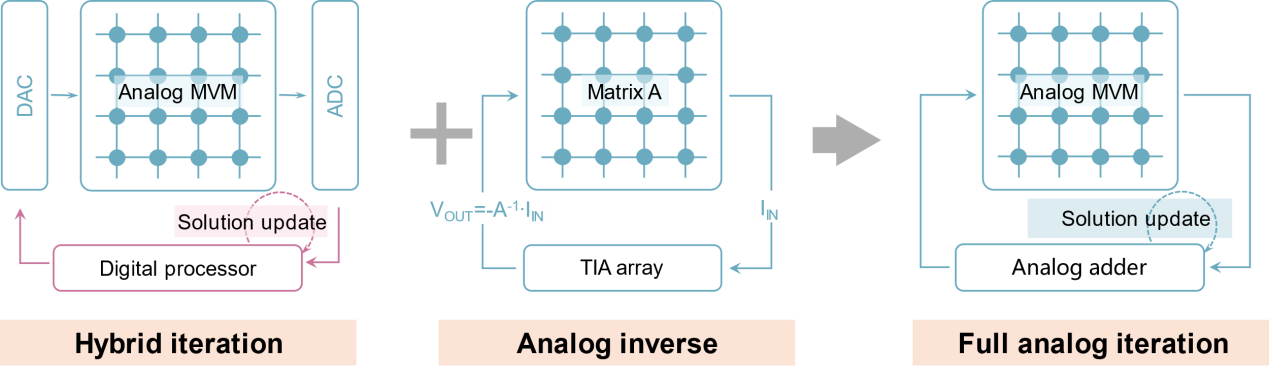

图2. 忆阻全模拟迭代计算

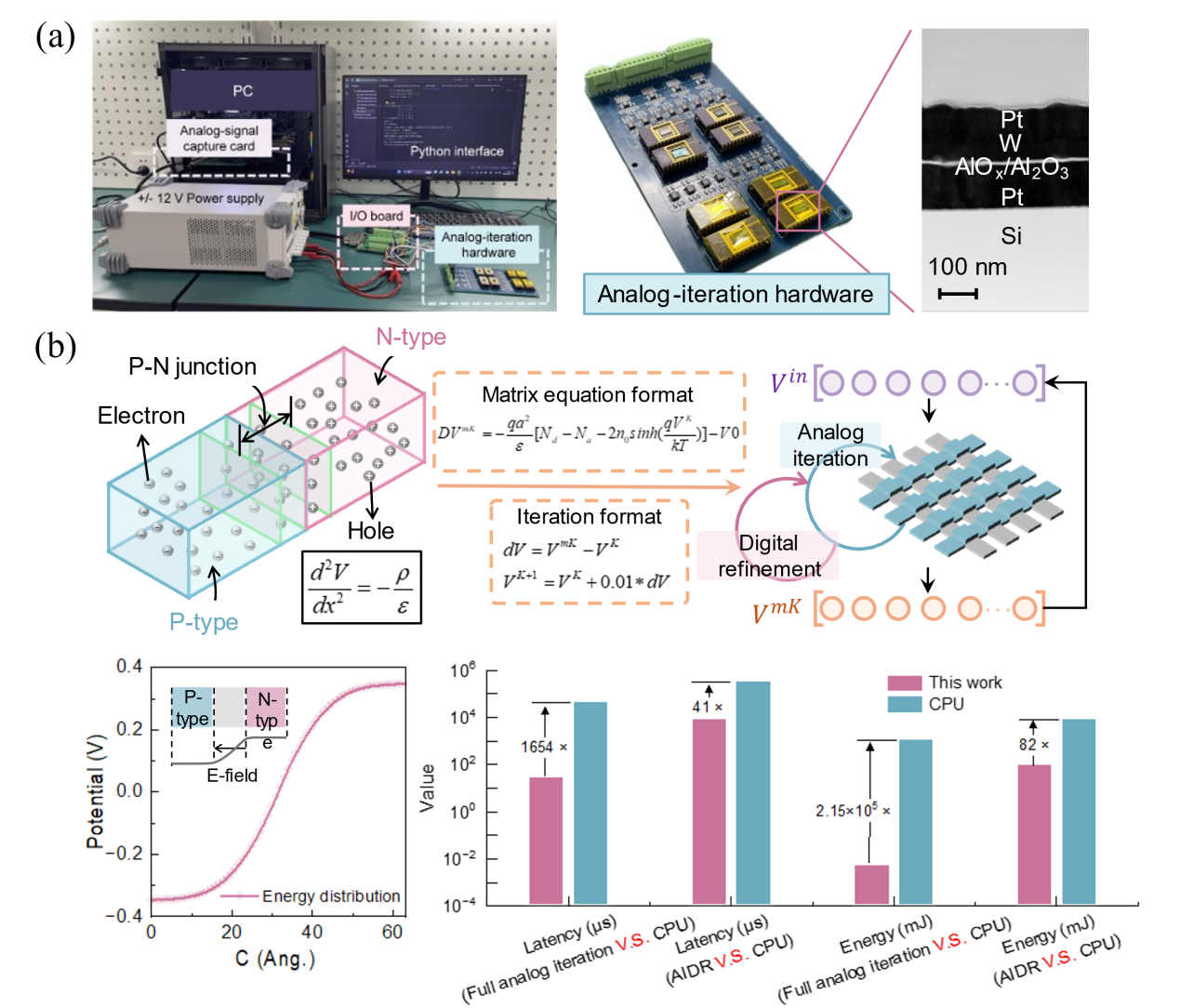

为解决上述难题,研究团队在前期忆阻矩阵方程求解器(Sci. Adv. 2023、IEDM 2023、IEDM 2024)的研究基础上,提出了将忆阻全模拟求解器与数字处理器融合,构建混合域异构矩阵方程求解系统的新思路。该系统可在忆阻阵列中执行全模拟迭代,以低时间复杂度生成初始解,进而利用数字处理器计算修正得到高精度解(Analog Iteration with Digital Refinement, AIDR)。实验上,团队制备了一种基于二值忆阻器的迭代求解电路,在模拟域内实现了可变精度的矩阵方程数值迭代计算。该电路具有可扩展的拓扑结构和O (1) 计算时间复杂度,在基准求解测试中取得了10-3的求解误差,从而支撑AIDR系统在亚线性时间复杂度(O (Nb),b = 0.38)下实现误差低于10-12的高精度求解。将AIDR系统用于扩散方程求解、硅P-N结平衡态模拟等计算任务中进行性能评估,结果表明在达到与商用CPU(Intel Core i5-13600K)相当求解精度(双浮点计算精度)时,系统实现了的41-128倍求解速度提升以及81-160倍的能耗降低。

该项研究不仅为基于忆阻器构建低时间复杂度、高精度浮点计算系统难题提供了有效方案,所设计的忆阻模拟迭代电路还可以作为实现大规模集成的求解器芯片的核心模块。研究成果有望进一步应用于计算建模、机器人定位与地图构建等场景,开拓忆阻存算一体技术在科学计算、具身智能等重要领域的应用潜力。

图3. (a)所构建的AIDR求解系统及忆阻全模拟迭代电路;(b)基于AIDR系统的硅P-N结平衡态模拟及求解性能评估

华中科技大学为论文第一完成单位和唯一通讯单位,集成电路学院博士后李健聪和博士研究生薛亦白为共同第一作者,李祎教授和缪向水教授为共同通讯作者,香港智能晶片与系统研发中心陈佳博士参与了本工作。

该研究工作得到了科技部国家重点研发计划、科技创新2030重大研究计划、华中科技大学基础研究支持计划、湖北省自然科学基金计划的资助,以及国家集成电路产教融合创新平台、先进存储器湖北省重点实验室等平台的支持。

论文信息:

J. Li, Y. Xue, Y. Li, et al. Fully analog iteration for solving matrix equations with in-memory computing. Science Advances, 11, eadr6391, 2025.

https://www.science.org/doi/10.1126/sciadv.adr6391