近日,我院博士生汪志城、明达在集成电路工程系谭旻研究员指导下,提出光电融合控制新方法打破国际微环波长锁定速度记录并大幅减小了电学控制部分面积,相关论文发表在光学旗舰期刊Optics Express和光通信顶级期刊Journal of Lightwave Technology上,论文题目分别为“ Resolving the scalability challenge of wavelength locking for multiple micro-rings via pipelined time-division-multiplexing control”(以下简称论文一)及“ An electronic-photonic converged adaptive-tuning-step pipelined time-division-multiplexing control scheme for fast and scalable wavelength locking of micro-rings(以下简称论文二)”。我校为论文第一和通讯作者单位,谭旻研究员为论文通讯作者,合作作者包括光电学院博士研究生汪宇航、物理学院王星泽教授、国光张新亮教授、上海交通大学邱辞源副教授及国家信息光电子创新中心肖希博士。

背景和挑战

近几年硅基光电子(硅光)技术不断发展,促进光学互连逐步替代电学互连,克服传统电学互连在散热、带宽、损耗等方面的固有缺点。然而硅光器件面临着热稳定性、工艺偏差等众多挑战,且以上挑战难以仅仅通过改进器件制备得到解决。将光子集成和集成电路相结合的光电融合技术有望解决以上挑战,是后摩尔时代集成电路的重要发展方向。

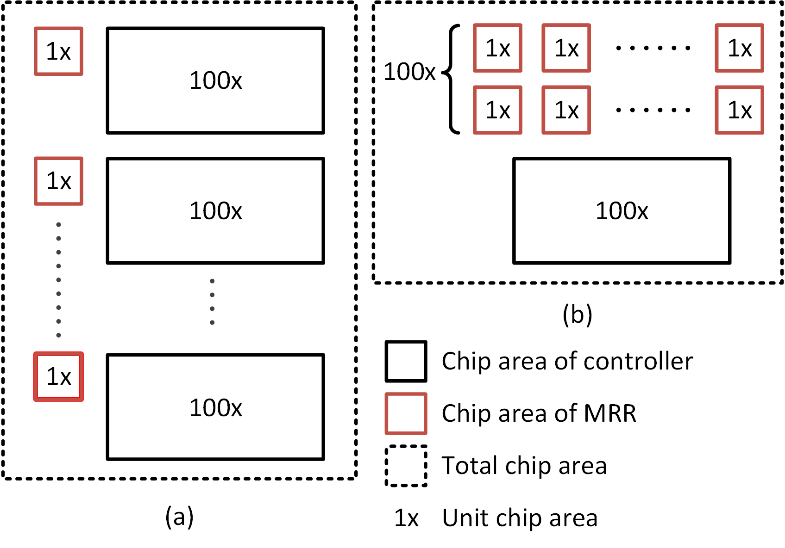

微环谐振器是最基础的硅光器件之一,其在光子领域重要性可以类比微电子领域的晶体管,能够实现调制、滤波、开关等各种核心光互连功能单元,是实现高密度、低功耗光互连的核心器件。除此之外,微环在生物传感、量子通信等领域也有重要应用。但是微环的状态稳定性极易受到环境温度、工艺偏差以及输入激光抖动等随机因素影响,且以上因素无法通过工艺制备消除,闭环反馈是维持微环稳定性的唯一手段。在闭环反馈环路中,控制电路面积一般远大于微环面积。给每个微环提供单独的控制电路将大大增加整体芯片整体面积及功耗(图1a),严重限制微环的大规模阵列应用。如何在不影响速度等性能参数的情况下减小微环控制电路面积是亟需解决的挑战。

图 1 (a)单控制器单微环方案的面积示意图;(b)单控制器多微环方案的面积示意图

解决方案

针对电学控制部分面积和微环锁定速度的问题,谭旻课题组提出了流水线时分复用和自适应步长光电融合控制新方法,大幅减小电学控制面积并打破国际上微环波长速度记录。

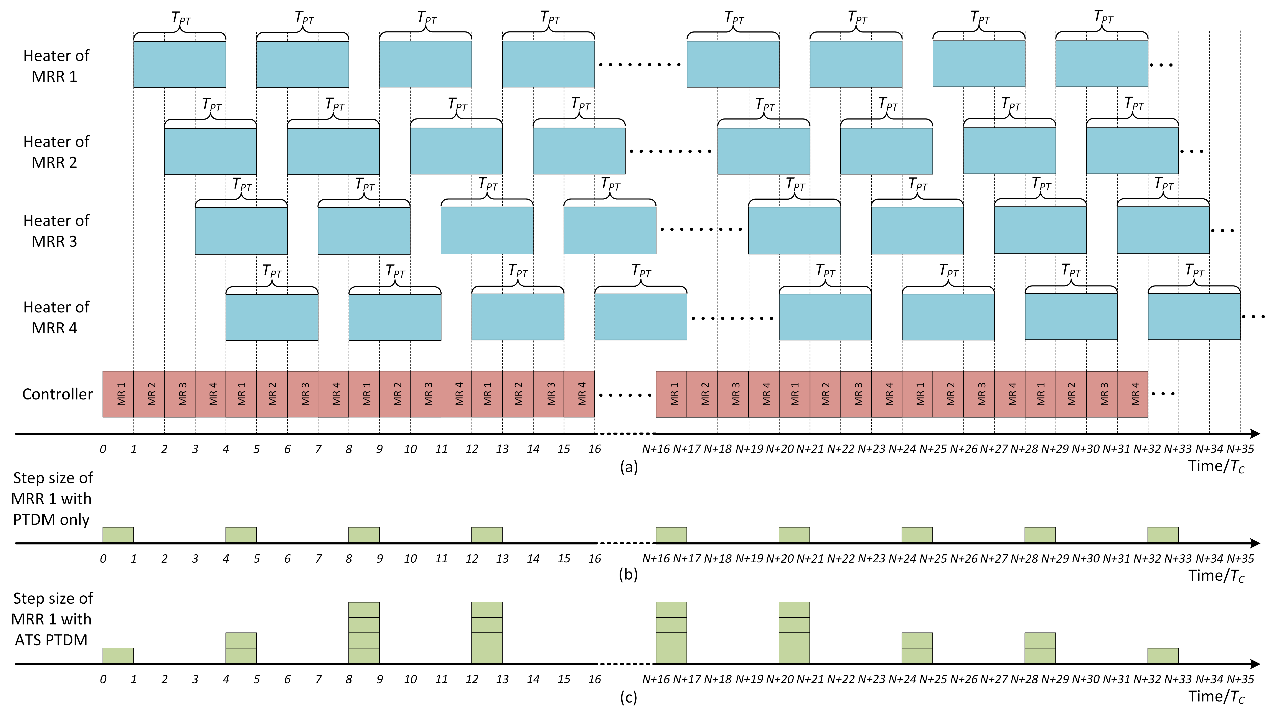

图 2 流水线时分复用技术与自适应步长技术相结合的时序图

论文一提出了流水线时分复用技术,在优化单环锁定速度的同时实现单个控制器控制多个微环谐振器(图1b)。该技术利用控制电路响应速度(通常为μs量级)和热调响应速度(通常为100μs量级)之间的失配,使控制电路和热调器依次按照流水线的方式循环工作(图2)。该方案具有极佳的可扩展性,有潜力拓展到几十甚至上百个微环的阵列应用中。以上方案通过混合集成的光电融合芯片得到了实验验证。与已有文献相比,该方案仅需一个控制器就能够实现对四个微环的同时锁定,并通过系统和电路的优化设计实现了15 nm/s的正弦信号锁定追踪及30 nm/s的阶跃信号锁定追踪,在满足激光抖动、温度变化、工艺偏差等全方面稳定性要求情况下突破国际上微环波长锁定速度记录。

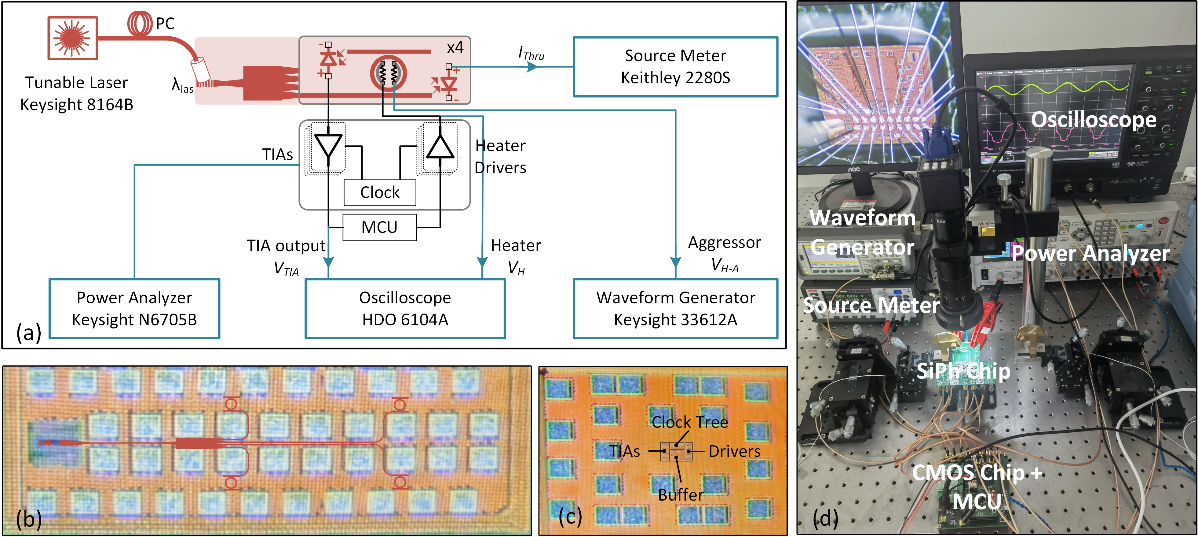

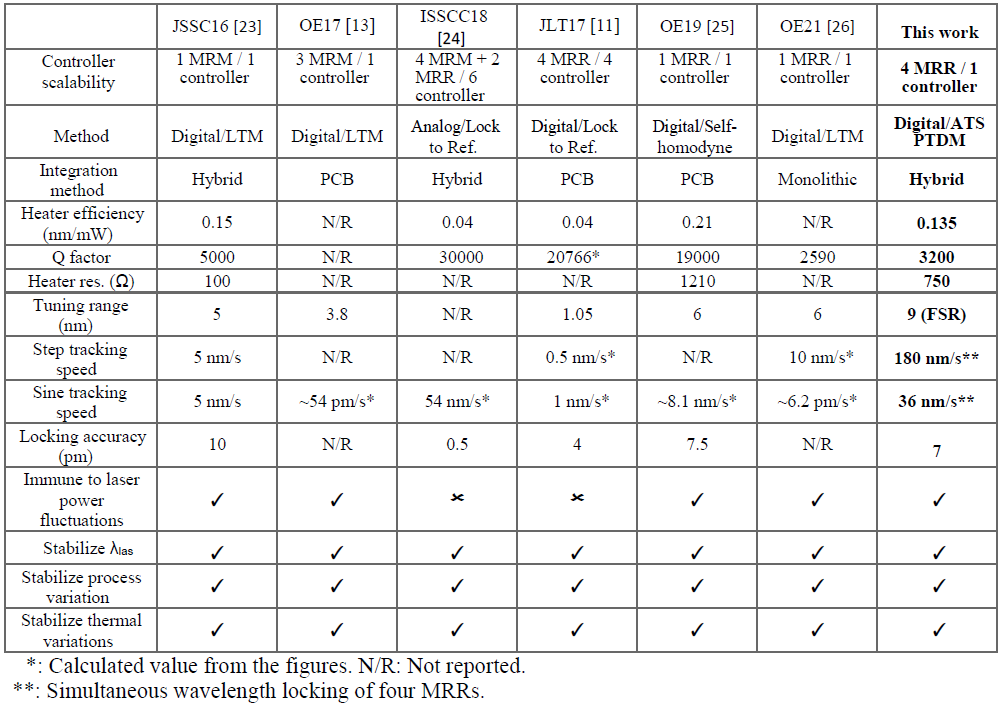

论文二提出了自适应步长技术,打破了锁定方案的精度与速度折衷(图2),在维持锁定精度的同时提升了波长锁定速度,并通过与流水线时分复用技术的结合有可能进一步提升系统可扩展性。相比于单独使用流水线时分复用技术的波长锁定系统,自适应步长技术的应用只增加了少量的动态功耗,几乎没有增加硬件开销。以上方案通过混合集成的光电融合芯片得到了实验验证,其中电芯片部分采用130nm CMOS标准工艺实现,光芯片部分采用IHP 0.25-µm photonic BiCMOS工艺实现。与已有文献相比,该方案实现了36 nm/s的正弦信号锁定追踪及180 nm/s的阶跃信号锁定追踪(表1),在满足激光抖动、温度变化、工艺偏差等全方面稳定性要求下实现了对微环波长锁定速度记录的大幅超越。图3展示了相关的光子芯片、电子芯片及测试系统示意图和实物图。

图 3 (a)四微环谐振器波长锁定系统的测试设置示意图;(b)微环阵列光子芯片;(c)波长锁定电子芯片;(d)四微环谐振器波长锁定系统的测试设置照片

表 1 性能对比

近年来,谭旻研究员领导的光电融合芯片实验室通过集成电路设计和光子集成两个不同领域的有机结合,提出了以反馈为中心的光与电回路级融合技术演进路线图,开拓了光电融合集成回路设计交叉学科研究新领域,在JSSC、TIT、JLT、OE、TCAS-I、ISCAS等国际一流期刊和会议上发表论文30余篇,申请及获取国内外专利30余项。

本研究工作得到了国家重点研发计划(2018YFA0704400)的资助。

原文链接:

https://ieeexplore.ieee.org/document/9783192

https://doi.org/10.1364/OE.459927